您现在的位置是:主页 > 硬件测评 > 硬盘测评 >

三星3D V-NAND技术解析:引领闪存的新时代

发布时间:2013年08月22日 08:30:09 硬盘测评 人已围观

简介三星在过去两年已成为全球最大的NAND供应商,凭借强大的生产能力和顶尖的技术实力。本月初,三星宣布成功量产全球首款3D垂直闪存V-NAND,并在本月中旬推出了企业级V-NAND闪存,进一...

在过去的两年里,三星已经成为全球领先的NAND闪存供应商,凭借出色的生产能力和顶尖的技术实力,稳居行业首位。本月初,三星宣布成功量产全球首个3D垂直闪存V-NAND,并在本月中旬推出了相关的企业级V-NAND闪存。尽管海力士、SanDisk、美光和东芝等其他厂商也在推行各自的垂直闪存项目,但三星在量产方面已经走在了前面,从而获得了更为显著的竞争优势。

三星的V-NAND每个die的容量为128Gb(16GB),利用3D堆叠技术,最多可以实现24层的die堆叠,从而使得总容量可达到384GB。此外,三星还表示V-NAND闪存在写入速度以及可靠性上都有超过两倍的提升。

三星量产V-NAND垂直闪存的意义何在?它是如何实现的?这对整个NAND产业又会带来什么样的影响?Anandtech网站对此进行了深入分析。

传统NAND面临的挑战:提升容量需更先进制程,伴随而来的是性能下降

自从2008年Intel推出X25-M SSD以来,SSD的价格显著下降,当时80GB SSD的价格高达600美元,如今同样的预算却可购买到三星或美光的1TB SSD。摩尔定律不断推动电子产品的进步,晶体管尺寸不断减小,NAND闪存的密度不断提升,价格也相应降低。

然而,晶体管缩小导致的后果是NAND的可靠性与性能逐渐下降。以IMFT近年来的NAND产品的P/E循环及编程时长为例,如下图所示。

不同工艺下的闪存擦写次数及编程时间

在50nm制程时期,P/E次数达到10000次,编程所需时间仅为900us。然而,随着制作工艺的进步,P/E次数已由1000次降低至5000次,再降至3000次。这只是MLC的情况,如果是TLC,P/E次数更是降至1000次。

这一现象的根本原因在于基本的物理特性。2bit MLC每个单元需存储2bit数据,仅需一小部分电子,而3bit MLC(即TLC)中的每个单元储存方式在NAND缩小后则变得复杂,如果进入到14/15/16nm阶段,情况将更加严峻。

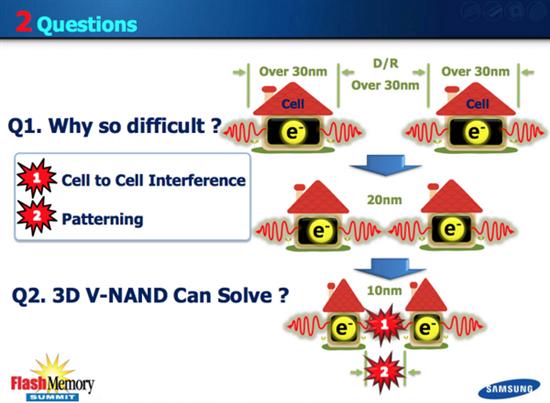

三星的简洁说明

在这些微小变化的测量上,特别是在NAND单元日益缩小并互相靠近的情况下,挑战更为显著。20nm工艺之后,单元间的干扰加剧,而在50nm工艺阶段,这些问题之前可借助主控和优质的NAND得以缓解。如今我们已看到,SSD主控需要执行更多ECC和DSP相关工作,以确保数据能被准确读写。

通过更先进制程继续生产传统NAND的路线即将面临瓶颈,目前的工艺预计仅能持续一到两代,之后继续缩小单元的可能性很小。

那么,NAND未来的出路在哪里?答案就是V-NAND技术。三星通过电荷捕获闪存(charge trap flash)技术成功推出3D闪存。