您现在的位置是:主页 > 硬件测评 > CPU测评 >

AMD新一代推土机处理器架构详细信息与性能揭秘

发布时间:2010年04月02日 12:34:56 CPU测评 人已围观

简介AMDZone.com独家报道了来自AMD全球服务器与工作站业务经理John Fruehe的信息,揭示了下一代处理器架构“推土机”(Bulldozer)的技术细节和实际性能。这些信息为AMD未来在处理器市场的竞争...

根据AMDZone.com的独家消息,来自AMD服务器与工作站全球业务经理John Fruehe透露了即将推出的下一代处理器架构“推土机”(Bulldozer)的相关信息,涵盖了更加详尽的架构技术和性能表现。

在被问及为何此时发布这些信息时,John Fruehe表示,尽管推土机架构的处理器还有一段时间才会上市,但他们对新产品充满信心,并对Intel的下一代芯片(Sandy Bridge)并不在意。

一、推土机架构概述

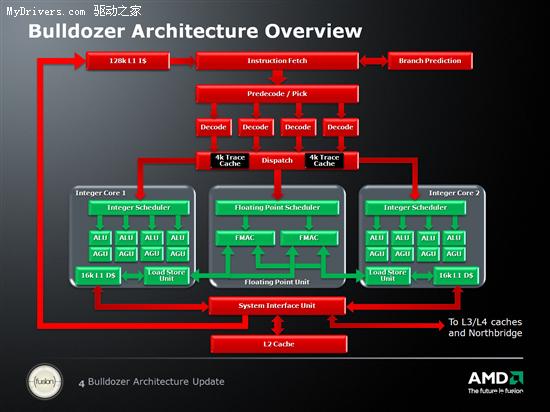

在去年11月底的年度分析师会议上,AMD首次介绍了推土机架构的若干技术特性,随后我们也进行了相应的分析。今天,AMD进一步提供了架构示意图。

每个推土机模块内含有两个整数核心和一个浮点单元。每个整数核心配备四条完整的整数管线,每条管线内部有一个算术逻辑单元(ALU)和一个地址生成单元(AGU),可同时处理x86整数指令、存储操作以及SSE、AVX整数指令,这被认为是一个重要的进步。

浮点单元配置了两个128位的FMAC单元,支持新的积和熔加运(FMA)指令或者执行浮点加法和乘法,这样设计不仅能降低功耗,还能提升基本操作的吞吐率。AMD解释称,两个FMAC单元可以被两个整数核心的两个线程并发使用,也可以被单一线程循环调用。

每个整数核心还设有16KB的一级缓存和载入存储单元(LSU),LSU负责协调来自自身整数核心和浮点单元的所有存储请求,每个核心可同时进行两个加载及一个存储操作,最大支持128-bit。相较于K10架构,推土机的LSU功能还支持数据和地址的预测。

为了减少分支预测错误所带来的延迟,分支预测单元进行了改进,能够在每个时钟周期内预测多个分支并发起代码预取。

此外,模块的性能提升还得益于各单元可以在不同的频率下运行,闲置的子单元可以关闭并调整缓存大小(例如将四路16KB的一级缓存关闭为双路8KB),每个子单元的载入和功耗通过一个电源控制器进行监测,这一机制被称为应用电源管理(APM)。

最后的架构设计包括五级缓存:

- 零级缓存:每个线程(或核心)4KB 8路关联;

- 一级缓存:每个核心16KB 4路关联数据缓存,延迟为一个时钟周期;每个模块128KB 4路关联;

- 二级缓存:每个模块2MB 8路关联,两个核心共享,全速访问;

- 三级缓存:所有核心共享8MB,延迟24个时钟周期,每个时钟周期最多处理两个请求;

- 四级缓存:桌面黑盒版以及服务器Opteron通过芯片堆栈增加四级缓存,容量可达32MB或64MB。

二、新的接口与制造工艺

在基于32nm SOI工艺的早期试产中,推土机核心显示出极高的可靠性,因此AMD正在探索使用28nm Bulk工艺进行小批量生产,但尚未确认是否会最终采用28nm。

Tags: 快讯

相关文章

随机图文

AMD桌面六核Thuban提前体验:惊艳瞬间解析

AMD和Intel的六核处理器在服务器市场已经销售一段时间,预计明年将进入桌面市...

《实测:龙之战争第二部与Phenom II X3 72

AMD于1月8日在CES发布了Dragon平台和Phenom II X4处理器,首发包括AM2+接口的940黑盒版...

Phenom II X6 1055T六核性能测试与超频评估

AMD发布了首批两款Phenom II X6系列六核心桌面处理器,其中高端型号X6 1090T备受关...

强劲性能解析:45纳米E5200评测报告

45nm奔腾双核是Intel在中低端CPU市场的重要产品。随着制程工艺的转型,从65nm到...